Smash Kirby

Bob-omb

Intel, AMD, ARM, TSMC, and Samsung all support 'Chiplets' for future processor design

This seems pretty interesting and I wonder if future consoles will use this design as this seems similar to the normal setups.

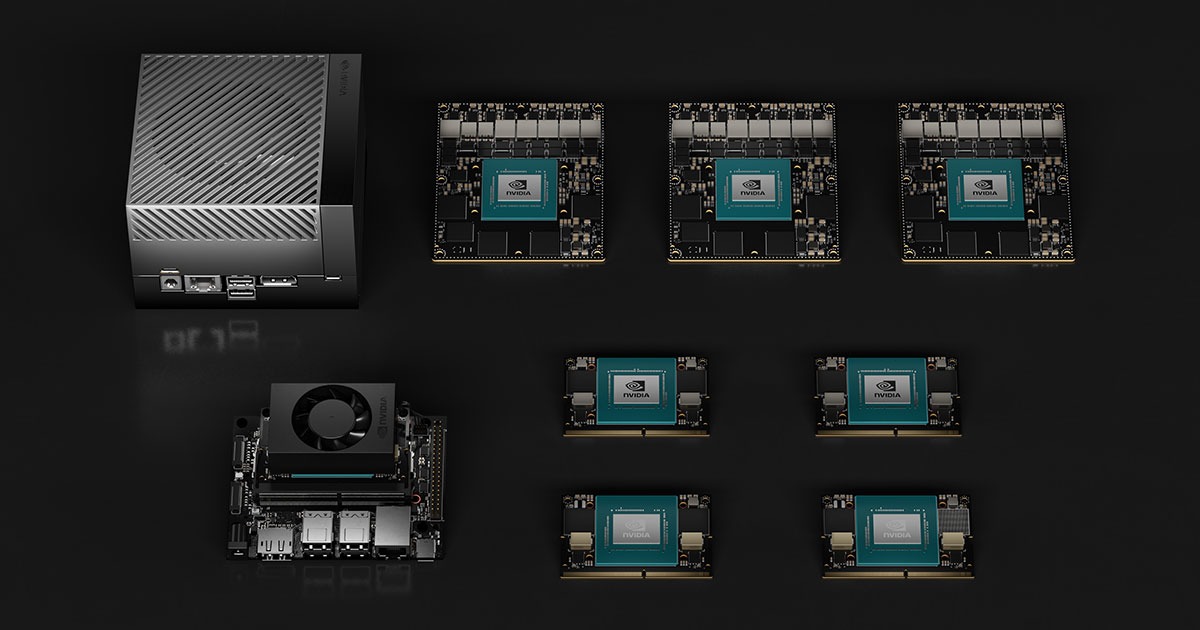

Intel, AMD, ARM, Samsung, Qualcomm, and TSMC, have come together to form a common and open standard for "Chiplets". A much smaller version of processors, chiplets have witnessed a massive growth in design, development, and adoption in the last few years. The Universal Chiplet Interconnect Express (UCIe), intends to standardize die-to-die interconnects for chipset designs with an open-source approach.

All the three leading-edge foundries, and dominant manufacturers of silicon wafers, have come together to announce that they are forming a new and open standard for chiplet interconnects. The UCIe hopes to simplify and standardize die-to-die connections in hardware and software. Eventually, such an approach could help designers and manufacturers of chips, CPUs, chipsets, and SoCs to easily and efficiently "mix and match" chiplets from different companies and create custom solutions.

Chiplets are essentially tiny blocks of integrated circuits. They are smaller than a traditional, monolithic CPU, and generally perform fewer tasks. Chiplets often lighten the load of the central processing cores. Interestingly, CPUs themselves can be designed as chiplets. In fact, Intel, ARM, and AMD are currently leading the development of processors which contain multiple chiplets. These new generations of CPUs have some performance cores and some efficiency cores. Other chiplets that are part of the package, include the integrated GPU, NPU, and perhaps even RAM and internal storage.

This seems pretty interesting and I wonder if future consoles will use this design as this seems similar to the normal setups.